L'evoluzione del PCIe: da 5.0 a 6.0

PCIe è stato l'interconnessione spinale per lo storage e gli acceleratori ad alte prestazioni per molti anni. Il salto da PCIe 5.0 a PCIe 6.0 non è solo un incremento numerico: rappresenta uno spostamento delle aspettative di segnale, codifica e livello di sistema. Dove PCIe 5.0 si affida a migliori sistemi di segnalazione analogica e codifica familiare, PCIe 6.0 introduce il segnale PAM4 e la correzione di errore in avanti robusta, consentendo tassi di dati grezzi molto più elevati per corsia.

Comprendere questa evoluzione aiuta a spiegare perché prevedono SSD e progettisti di sistema sono eccezionali. Il cambiamento è sia fisico (diverse caratteristiche elettriche) che logico (nuove funzionalità di protocollo per mantenere l'affidabilità a velocità più elevata). Per gli architetti questo significa rivisitare i budget dei canali, i disegni PHY e la logica del controller per individuare l'interfaccia.

Doubling the Speed: Come PCIe 6.0 Ridefinisce la larghezza di banda

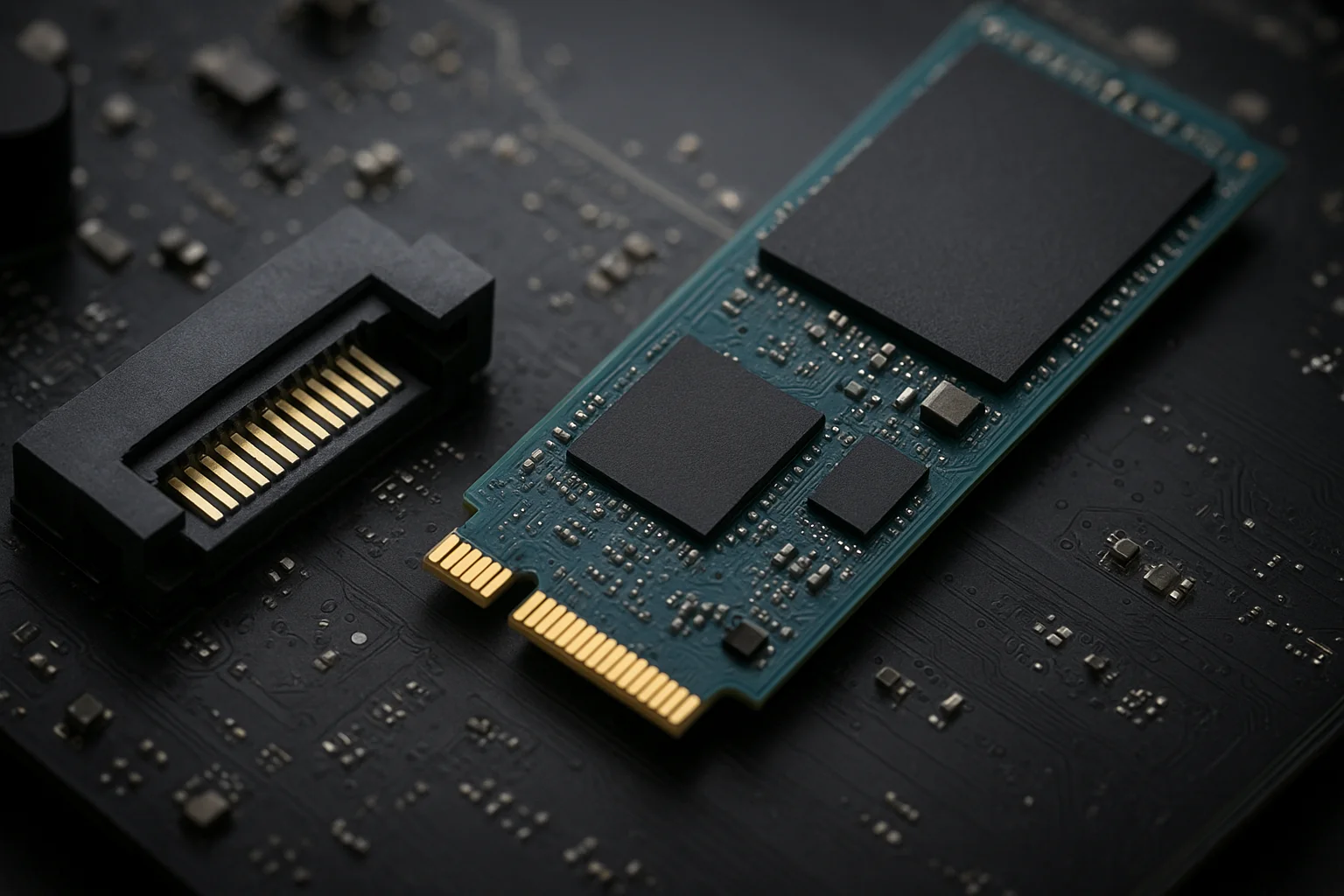

PCIe 6.0 parallelo la larghezza di banda per-lane rispetto a PCIe 5.0 spostandosi a PAM4 (modulazione di ampiezza del polso a quattro livelli) a velocità di segnalazione più elevata. L'esito pratico per M.2, U.2 e l'add-in card NVMe SSDs è un passaggio nel throughput disponibile, che può essere applicato alla larghezza di banda sequenziale grezza o aggregare I/O attraverso codice e core fuso.

Di seguito è riportato un confronto conciso che mette in evidenza i più significativi sistemi di numeri progettisti e ingegneri di storage utilizzati durante la pianificazione di aggiornamenti o nuovi prodotti.

| Metrico | PCIe 5.0 (per corsia) | PCIe 6.0 (per corsia) |

|---|---|---|

| Segnale | NRZ (binary) | PAM4 (4 livelli) |

| Tasso di dati greggio | 32 GT/i | 64 GT/s |

| Traduzione | ≈16 GB/s | ≈32 GB/s |

| Gestione degli errori | CRC, retry | FEC + CRC |

La tabella mostra perché PCIe 6.0 è attraente: Condividi su Twitter per corsia, più correzione di errore aggiunta che consente un trasferimento affidabile su fattori di forma esistenti con un'attenta progettazione del canale.

SSD Performance Gains: Real-World Impact and Bottleneck Removal

La larghezza di banda PCIe superiore si traduce in potenziale offrendo a livello SSD, ma l'impatto reale dipende da più sottosistemi. Le moderne unità NVMe sono limitate non solo dalla larghezza di banda dell'interfaccia, ma anche dal parallelismo del controller, dalle prestazioni del pacchetto flash NAND, algoritmi del firmware e dalla gestione della CPU/memoria lato host di I/O.

Per rendere significativo PCIe 6.0 per gli utenti, i fornitori devono affrontare queste aree:

- Parallelismo del controller - Aumentare i canali interni e migliorare la pianificazione per alimentare l'interfaccia.

- NAND front-end - Utilizzare NAND più veloce, conteggi di canali più alti, o stacking avanzato per evitare NAND diventare il collo di bottiglia.

- Gestione firmware e coda - Ottimizzare la gestione dei comandi NVMe, ridurre latenza nei percorsi di espansione e sfruttare il parallelismo multi-queue.

Per gli integratori di sistema valutare gli aggiornamenti, prendere in considerazione questi esempi pratici di dove PCIe 6.0 conta di più:

- I carichi di lavoro con throughput sequenziale sostenuto (movimento di dati su larga scala, backup, streaming multimediale) vinceranno quasi lineari se l'SSD interni scalano di conseguenza.

- I carichi di lavoro transazionali misti (databases, I/O virtualizzati) beneficiariano di un aumento degli IOPS aggregati quando il parallelismo e gli stack host sono sintonizzati.

- Le pipeline di formazione AI/ML che dannono enormi set di dati da storage ad acceleratori possono ridurre le finestre di caricamento dati e aumentare l'utilizzo dell'acceleratore.

Regola rapida del pollice: se l'attuale SSD sta saturando il suo collegamento PCIe 5.0 per i trasferimenti sostenuti, un SSD PCIe 6.0 con un'architettura interna comparabile dovrebbe fornire fino a due volte il throughput—forniti vincoli termici e NAND sono affrontati.

Efficienza energetica e Integrità dei dati: Bilanciamento della velocità con stabilità

I tassi di segnalazione più elevati aumentano tipicamente il consumo di energia e l'uscita termica. PCIe 6.0 lo contrasta utilizzando FEC (previa correzione di errore) per mantenere l'affidabilità del collegamento senza retras eccmissioniessive, che possono salvare paradossalmente la potenza a livello di sistema evitando i passaggi maturatuti. Tuttavia, i progettisti devono bilanciare tre priorità concorrenti: throughput, potere e apparenza dei dati.

I fornitori di misure pratiche e i rischi di sistema adottare adottare:

- Implementare gli stati di potenza adattativi e la formazione di collegamento dinamico per ridurre la potenza del liquido mantenendo le corsie ad alta velocità pronte.

- Migliorare le politiche di raffreddamento e di accettazione termica nel firmware SSD per sostenere l'alta percentuale senza fingerere i limiti termici.

- Diagnostica FSE di levaggio: utilizzare statistiche di errore da FEC per guidare la manutenzione preventiva o il ri-rating adattativo delle velocità di collegamento.

Da un punto di vista operativo, gli amministratori dovrebbero monitorare sia le metriche di livello di collegamento (conti di correzione FEC, eventi di riqualifica) che la telemetria SSD (temperature, tassi di errore NAND). Il monitoraggio proattivo consente di effettuare una piccola riduzione del throughput per l'affidabilità a lungo termine quando necessario.

The Road Ahead: Role di PCIe 6.0 in Next-Gen Computing e Storage

PCIe 6.0 è un ponte verso applicazioni sempre più basate sui dati. Non permetterà solo sSD più velocità, ma influenzano anche le topologie del sistema: storage disaggregato, NVMe-oF su tessuti, e un accoppiamento più stretto tra storage e acceleratori. Perché?

- Convergenza della piattaforma - CPU, acceleratori e licenze di archiviazione in evoluzione insieme per rimuovere le bancarelle I/O.

- Software di regolazione - I sistemi operativi, ipervisori e gli stack di storage aggiungeranno ottimizzazioni per velocità di collegamento più elevata e un maggiore parallelismo.

- Nuovi prodotti - SSD progettato per saturare PCIe 6.0 in server di fascia alta, e unità più modeste che ricevono l'interfaccia per la testata e la protezione futura.

Consigli utili per la pianificazione della migrazione dei team:

- Carico di lavoro di Benchmark oggi per identificare se il collo di bottiglia è il collegamento PCIe o l'architettura SSD interna Priorizzare gli aggiornamenti in cui il throughput sostenuto è attualmente limitato dall'interfaccia host.

- Durante la convalida dell'hardware PCIe 6.0, incluso test di conformità del canale, test di stress termico e monitoraggio FEC/error nel pianoforte di accettazione.

- Pianificare gli aggiornamenti del firmware e del driver: i guadagni spesso da aggiornamenti coordinate tra host driver, firmware SSD e sistema BIOS.

Adottare PCIe 6.0 sarà evoluzionario: i primi adottivi nei data center spingeranno i confini, mentre l'adozione mainstream seguirà come NAND e i controllori catturano. Per i creatori di contenuti, gli operatori di database e i team AI, PCIe 6.0 offre un headroom delle prestazioni concrete; per gli architetti, richiede un'attenta progettazione a livello di sistema per convertire la larghezza di banda raw in beneficiari applicativi misurabili.