De evolutie van PCIe: Van 5.0 tot 6.0

PCIe is al jaren de ruggengraatverbinding voor high-performance opslag en versnellers. De sprong van PCIe 5.0 naar PCIe 6.0 is niet alleen een numerieke toename: het vertegenwoordigt een verschuiving in signaal, codering en systeem-niveau verwachtingen. Waar PCIe 5.0 afhankelijk was van verbeterde analoge signalering en vertrouwde coderingssystemen, PCIe 6.0 introduceert PAM4 signaal en robuuste voorafse foutcorrectie, waardoor veel hogere ruwe gegevens per rijstrook.

Het verwerken van deze evolutie helpt uitnemend waar SSD leveranciers en systeemmontwerpers enthousiast zijn. De verandering is zowel fysiek (verchillende elektrische merken) als logisch (nieuwe protocol functies om de inzet bij hoge cijfers te behouden). Voor architecten betekent dit het nieuw bekijken van Kanaal budgetten, PHY ontwikkelen, en controller logica om de interface volledig te benutten.

Verdubbelen van de snelheid: Hoe PCIe 6.0 Redefines Bandbreedte

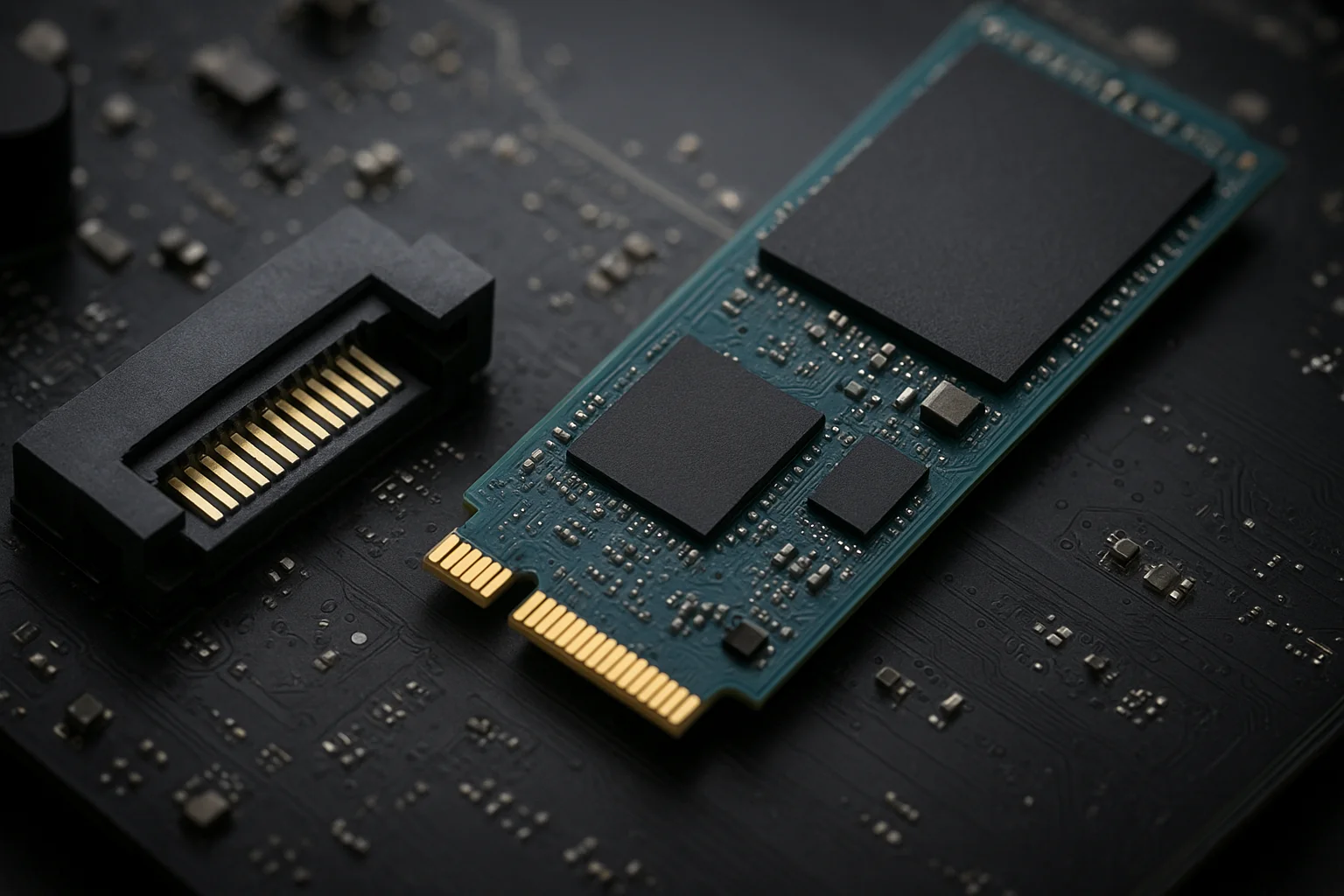

PCIe 6.0 verdubbelt effect de bandbreedte per lijn in vergelijking met PCIe 5.0 door bij hoge tekenennloot naar PAM4 (pulsamplitudemodulatie op vier niveaus) te gaan. De praktische uitkomst voor M.2, U.2 en add-in kaart NVMe SSD's is een stap verandering in beschikbare doorgang, die kan worden toegevoegd op ofwel ruwe sequentiele bandbreedte of het aggregeren van I/O over veel wachten en groeien.

Hieronder is een bekende vergelijking die de meest relevante nummers systeem ontwerpers en opslag ingewijden gebruiken bij het plannen van upgrades of nieuwe producten.

| Metrisch | PCIe 5.0 (per rijstok) | PCIe 6.0 (per rijstok) |

|---|---|---|

| Signalering | NRZ (binair) | PAM4 (4 niveaus) |

| Raw data rate | 32 GT/s | 64 GT/s |

| Effectieve bandbreedte (x4) | ≈16 GB/s | ≈32 GB/s |

| Fout bij handen | CRC, nieuwe zoon | FEC + CRC |

De tabel laat zien waarom PCIe 6.0 aantrekkelijk is: de effectieve bandbreedte verdubbelen per rijstrook, plus toegevoegde foutcorrectie die betrouwbare overdracht over bestaande vormfactoren met zorgvuldige kanaalontwerp mogelijk maakt.

SSD Performance Gains: Real-World Impact and Bottleneck Removal

Hogere PCIe-bandbreedte vertaalt zich in potentiele overwinningen op SSD-niveau, maar de reële impact is afhankelijk van meerdere subsystemen. Moderne NVMe drives worden niet alleen beperkt door interface bandbreedte, maar ook door controller parallelisme, NAND flash pakket prestaties, firmware algoritmen, en host-side CPU/geheugen behandeling van I/O.

Om PCIe 6.0 zinvol te maken voor gebruikers, moet leveranciers deze gebieden aanpakken:

- Controller parallelisme - Verhoog de interne kanalen en werk beter de planning om de interface te voeren.

- NAND front-end - Gebruik goedkope NAND, hoge kwaliteiten, of geavanceerde Stapels om te voorkomen dat NAND de bottleneck wordt.

- Firmware- en wachtrijbeheer - Optimaliseer NVMe command handling, verminder latency in completeren paden, en gebruik multi-queue parallelisme.

Voor systeemintegrators die upgrades ewaarderen, bekijk deze praktische voorbeelden van waar PCIe 6.0 het meest belangrijk is:

- Workloads met behoudende sequentiele doorgang (grootschalige dienstverlening, back-ups, mediastreaming) zullen bijna lineaire winsten zien als de SSD internals dieovereenkomst schalen.

- Gemengde transacties workloads (databases, gevirtualiseerde I/O) profiteren van hoge geaggregeerde IOPS wanner parallelisme en host stacks worden afgegeven.

- AI/ML training pijpen die grote datasets van opslag naar versnellers streamen, kunnen het dataloaden van vensters wijderen en het gebruik van versnellers verhogen.

Snelle vuistregel: als uw huidige SSD zijn PCIe 5.0-link verzadigen voor aanhoudende transfers, moet een PCIe 6.0 SSD met vergelijkbare interne architectuur tot twee keer de verwerkingscapaciteit en thermische en NAND-beperkingen opleveren.

Energie-efficiëntie en kwaliteit: Balancing Speed with Stability

Hogere tekenennelheden verhogen doorgangen het energieverbroek en de thermische uitgang. PCIe 6.0 tempert dit door gebruik te maken van FEC (forward error correction) om de aanwezigheid van de koper te behouden zonder buitensporige doorgiften, wat paradoxaal genoeg Stroom kan besparen op het niveau van het systeem door herhalingen te vermijden. Toch moeten ondernemers drie overeengekomen prioriteiten in evenwicht brengen: doorvoer, jacht en data-integratie.

Praktijkstatistieken die leveranciers en systeembouwers moeten nemen:

- Implementeer adaptieve vermogenstoestanden en dynamische koperingstraining om het stationair vermogen te verwijderen terwijl high-speed lanes staat te waarschuwen.

- Verbeteren van de koeling en thermische throttling gedrag in SSD firmware te ondernemen hoge doorvoer zonder het raken van theoretische grenzen.

- Hefboom FEC-diagnostiek: gebruik foutstatistieken van FEC om preventief onderhoud van adaptieve herclassificatie van verbindingennelheden te betalen.

Vanuit operationeel perspectief moeten beheerders zowel link-level metrics (FEC correctie counts, retrain events) als SSD telemetrie (temperatuur, NAND foutenpercentages) monitoren. Proactieve monitoring zorgt ervoor dat u een kleine verwerkingsregeling afwisselt voor ondernemerschap op lange termijn nodig heeft.

De Weg voorop: PCIe pluraliteit rol in Next-Gen Computing en opslag

PCIe 6.0 is een brug naar steeds meer data-hongerige toepassingen. Het zal niet alleen snellere SSD's mogelijk maken, maar ook systeemtopologieën beïnvloeden: schema's opslag, NVMe-oF over Stoffen, en strakkere samenwerking tussen opslag en versnellers. Verwacht deze trends:

- Platformsamenstelling - CPU's, versnellers en opslaginterfaces die samen evolueren om I/O kraampjes te verbergen.

- Softwareaanpassingen - Operating systemen, hypervisors, en opslag stacks zal bijdragen aan optimalisaties voor hoge link snelheden en toegekomen parallelisme.

- Nieuwe productniveaus - SSD's specifieke ontwerpen om PCIe 6.0 te verkopen in high-end servers, en meer schema's die de interface gebruiken voor headroom en Toekomstvriendelijke maken.

Actief advies voor teams die migratieplannen:

- Benchmark workloads van dag om te bepalen of uw bottleneck is de PCIe link van interne SSD architectuur. Prioriteer upgrades waar duurzaamheid doorvoer tijdelijk wordt beperkt door de host interface.

- Bij het valideren van PCIe 6.0 hardware, omvatten kanaal compliance testen, thermische stresstests, en FEC/error monitoring in uw acceptatieplan.

- Plan firmware en driver updates: echte overwinningen komen vaak van gecoördineerde updates over host drivers, SSD firmware en systeem BIOS.

Het adopteren van PCIe 6.0 zal evolutionair zijn: vroege adopters in datacenters zullen de grenzen verkopen, terwijl mainstream adoptie zal volgen als NAND en controllers inhaleren. Voor content makers, database operators en AI teams, PCIe 6.0 biedt beton prestaties hoofdruimte; voor architecten, het vereist zorgvuldige systeem-niveau ontwerp om ruwe bandbreedte om te zetten in meetbare toepassing onderdelen.