L'évolution de PCIe: de 5.0 à 6.0

PCIe est depuis de nombreuses années l'interconnexion de la colonne vertébrale pour le stockage haute performance et les accélérateurs. Le saut de PCIe 5.0 à PCIe 6.0 n'est pas seulement un accroissement numérique: il représente un changement dans la signalisation, l'encodage et les attentes au niveau du système. Lorsque PCIe 5.0 s'est appuyé sur une meilleure signalisation analogique et des schémas d'encodage familiers, PCIe 6.0 introduit la signalisation PAM4 et la correction d'erreur avant robuste, permettant des taux de données brutes beaucoup plus élevés par voie.

Comprendre cette évolution aide à expliquer pourquoi les fournisseurs SSD et les concepts de systèmes sont extrêmes. Le changement est à la fois physique (différentes caractéristiques électriques) et logique (nouveaux protocoles pour maintenir la fiabilité à des valeurs plus élevées). Pour les architectes, cela signifie revoir les budgets des canadiens, les conceptions de PHY et la logique de contrôle pour exploiter pleinement l'interface.

Doubler la vitesse: commentaire PCIe 6.0 redéfinit la bande passante

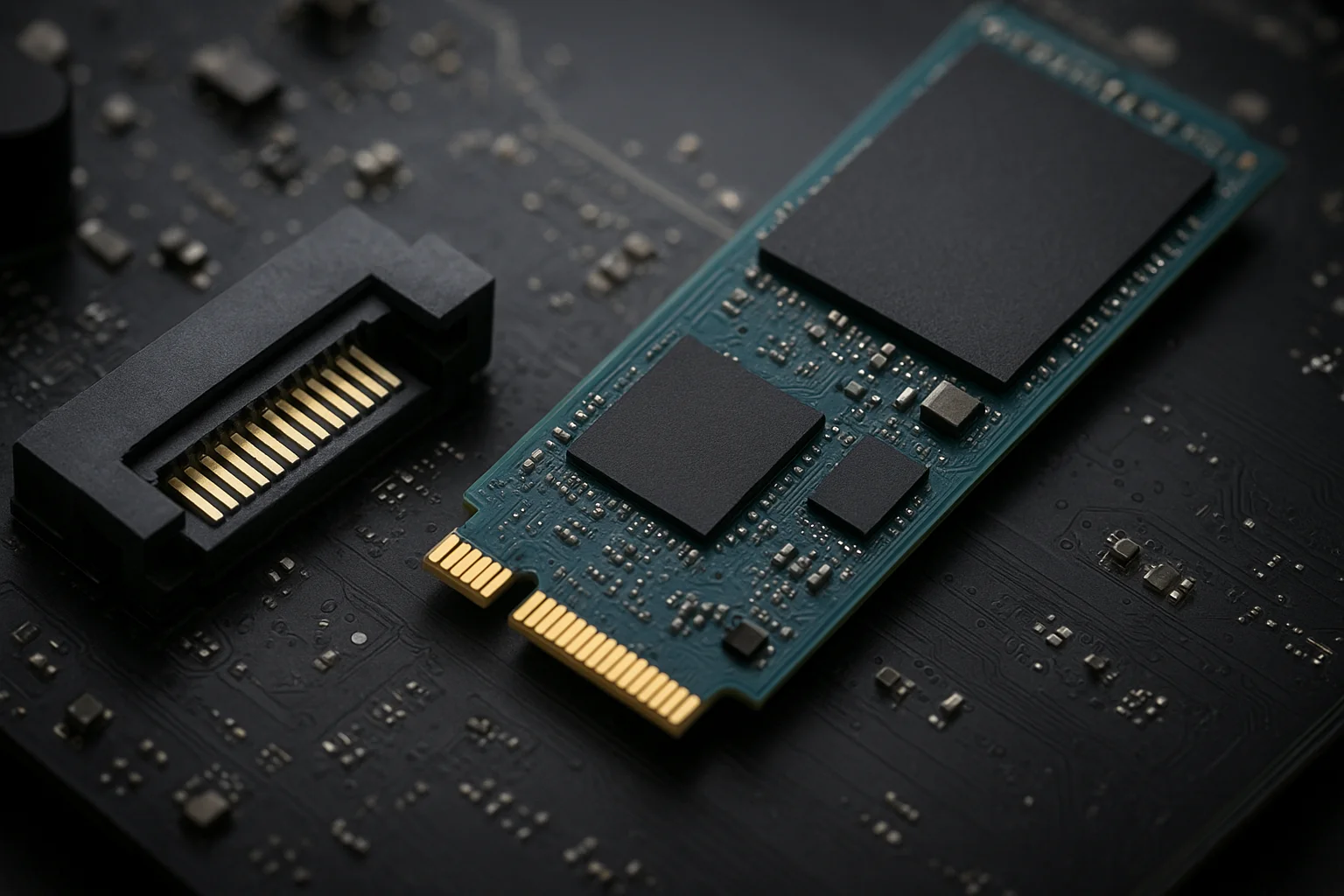

PCIe 6.0 double effet la bande passante par la voie par rapport à PCIe 5,0 en passant à PAM4 (modulation d'amplitude d'impulsion à quatre niveaux) à des valeurs de signalisation plus élevées. Le résultat pratique pour les cartes M.2, U.2 et add-in NVMe SSD est un changement d'étape dans le débit disponible, qui peut Ãatre appliqué soit à la bande passante séquentielle brute ou à l'approbation d'E/S dans de nombres fichiers d'attente et de coeurs.

Ci-dessous est une comparaison concise qui met en évidence les nombres les plus pertinents que les concepts de systèmes et les ingénieurs de stockage utilisent lors de la planification de mises à niveau ou de nouveaux produits.

| mécanique | PCIe 5.0 (par voie navigable) | PCIe 6.0 (par voie navigable) |

|---|---|---|

| Signalisation | NRZ (binaire) | PAM4 (4 niveaux) |

| Taux de données brutes | 32 GT/s | 64 GT/s |

| Bande passante efficace (x4) | ≈16 Go/s | ≈32 Go/s |

| Gestion des erreurs | CRC, chercheur | FEC + CRC |

Le tableau montre pourquoi PCIe 6.0 est attrayant: doubler la bande passante efficace par voie, plus correction d'erreur ajoutée qui permet un transfert fiable sur les facteurs de forme existants avec une conception de canal prudente.

SSD Gains de performance: Impact sur le monde réel et suppression du goulot d'étranglement

Une bande passante PCIe plus élevée se traite par des gains potentiels au niveau SSD, mais l'impact réel dépense de plusieurs sous-systèmes. Les lecteurs NVMe modernes sont limités non seulement par la bande passante de l'interface, mais aussi par le parallélisme du contrôle, les performances du paquet flash de NAND, les algorithmes de firmware, et la manipulation d'E/S côté hôtelier.

Pour que PCIe 6.0 soit significatif pour les utilisateurs, les fournisseurs doivent aborder ces domaines:

- Parallélisme du contrôle - Augmenter les canaux internes et améliorer la programmation pour améliorer l'interface.

- Avant de NAND - Utilisez NAND plus rapide, le nombre de canaux plus élevés ou l'emploi avancé pour inviter que NAND doit le goulot d'étranger.

- Firmware et gestion des fichiers d'attente - Optimiser la gestion des commandes NVMe, faire la latence dans les chemins d'achèvement et exploiter le parallélisme multi-queue.

Pour les intégrateurs de systèmes qui évaluent les mises à niveau, il convient d'examiner ces exemples pratiques où PCIe 6.0 est le plus important:

- Les charges de travail avec un débit sequentiel souverain (mouvement de données à grande échelle, sauvegardes, diffusion multimédia) verront des gains presque linéaires si l'école interne SSD en consultation.

- Les charges de travail transactionnelles mixtes (bases de données, E/S virtualisées) bénéficiant d'un nombre acquis d'IPOS agréés lors du parallélisme et les piles d'hôtes sont régrés.

- Les pipelines d'investissement AI/ML qui diffusent des ensembles de données massives depuis le stock jusqu'aux accélérateurs peuvent produire le chargement des appareils et obtenir l'utilisation des appareils.

Règle générale: Si votre SSD actuel sature son lien PCIe 5.0 pour des transferts soutenus, un SSD PCIe 6.0 avec une architecture interne comparable devrait fournir jusqu'à deux fois le débit—à condition que les contraintes thermiques et NAND soient traitées.

Efficacité de la puissance et intégrité des données: équilibrer la vitesse et la stabilité

Les taux de signalisation plus élevés augmentent globalement la consommation d'énergie et la puissance thermique. PCIe 6.0 contredit cette situation en utilisant la FEC pour maintenir la fiabilité des liaisons sans retransmissions excessives, ce qui permet paradoxalement d'établir la capacité au niveau du système en invitant les transferts effectués. Néanmoins, les concepts doivent équilibrer trois priorités concurrentes: le débit, le pouvoir et l'intégrité des données.

Les fournisseurs et les constructeurs de systèmes doivent adopter les mesures pratiques suivantes:

- Mettre en place des états de puissance adaptative et une formation dynamique pour produire la puissance au ralenti tout en maintenant les voies à grande vitesse prêtes.

- Améliorer les politiques de renouvellement et de throttling thermique dans le firmware SSD pour maintenir un débit élevé sans frapper les limites thermiques.

- Tirer parti du diagnostic FEC: utiliser les statistiques d'errers de la FEC pour guider la maintenance préventive ou la réévaluation adaptative des valeurs de liaison.

D'un point de vue opérationnel, les administrateurs doivent surveiller à la fois les mesures de niveau de liaison (comptes de correction de la FEC, événements de recyclage) et la télémétrie SSD (temporature, taux d'errer NAND). La surveillance proactive vous permet d'échanger une petite réduction de débit pour une fiabilité à long terme au besoin.

Le rôle du PCIe dans l'informatique et le stock de prochaine génération

PCIe 6.0 est un pont vers des applications de plus en plus ennuyeuses. Il permettra non seulement d'accélérer les SSD, mais aussi d'influencer les topologies du système: stockage désagrégé, NVMe-oF sur les tissus, et couplage plus servi entre stockage et accélérateurs. Prévoyons ces tendances:

- Convergence des plaques - Les processeurs, les acquéreurs et les interfaces de stockage évolutif ensemble pour remplacer les décrochages d'E/S.

- Ajustements logiques - Systèmes d'exploitation, hyperviseurs et piles de stockage ajouteront des optimisations pour des visites de liaison plus élevées et un parallèle accru.

- Nouveaux plans de produits - SSD comprend spécifiquement pour sater PCIe 6.0 dans les serveurs haut de gamme, et des disques plus modestes qui utilisent l'interface pour la salle de tête et l'épreuve future.

Conseils pratiques pour les équipes qui planifient les migrations:

- Benchmark charge de travail aujourd'hui pour identifier si votre goulot d'étranglement est le lien PCIe ou l'architecture SSD interne. Privilège les mises à niveau lorsque le débit souverain est actuellement limité par l'interface hôtelière.

- Lors de la validation du matériel PCIe 6.0, inclus des tests de conformité de canal, des tests de contrainte thermique, et la surveillance FEC/errer dans votre plan d'acceptation.

- Planifier les mises à jour du firmware et du pilote: les gains réels proviennent de mises à jour coordonnées entre les pilotes hôteliers, le firmware SSD et le BIOS du système.

L'adoption du PCIe 6.0 sera évolutive: les premiers adoptants dans les centres de données repoussent les limites, tant que l'adoption générale suivra le rythme de rattrapage du NAND et des contrôles. Pour les créateurs de contenu, les opérateurs de bases de données et les équipes d'IA, PCIe 6.0 offre une salle de tête de performance concrète; pour les architectes, il faut une conception indépendante au niveau du système pour convertir la bande passante brute en avantages d'application mesurables.